Clock skew

In synchronous circuit clock skew (TSkew) can be defined as the difference in the arrival time between two sequentially-adjacent registers. Given two sequentially-adjacent registers Ri and Rj with clock arrival times at register clock pins as TCi and TCj respectively, then clock skew can be defined as :

TSkew i,j = TCi - TCj

Clock skew can be positive or negative. If the clock signals are in complete synchronicity, then the clock skew observed at these registers is zero.

Contents |

In circuit design

In circuit designs, clock skew (sometimes timing skew) is a phenomenon in synchronous circuits in which the clock signal (sent from the clock circuit) arrives at different components at different times. This can be caused by many different things, such as wire-interconnect length, temperature variations, variation in intermediate devices, capacitive coupling, material imperfections, and differences in input capacitance on the clock inputs of devices using the clock. As the clock rate of a circuit increases, timing becomes more critical and less variation can be tolerated if the circuit is to function properly.

There are two types of clock skew: negative skew and positive skew. Positive skew occurs when the transmitting register receives the clock earlier than the receiving register. Negative skew is the opposite: the receiving register gets the clock earlier than the sending register.

Harmful skew

Two types of violation can be caused by clock skew. One problem is caused when the clock travels more slowly than the path from one register to another - allowing data to penetrate two registers in the same clock tick, or maybe destroying the integrity of the latched data. This is called a hold violation because the previous data is not held long enough at the destination flip-flop to be properly clocked through. Another problem is caused if the destination flip-flop receives the clock tick earlier than the source flip-flop - the data signal has that much less time to reach the destination flip-flop before the next clock tick. If it fails to do so, a setup violation occurs, so-called because the new data was not set up and stable before the next clock tick arrived. A hold violation is more serious than a setup violation because it cannot be fixed by increasing the clock period. Positive skew and negative skew cannot negatively impact setup and hold timing constraints respectively (see inequalities below).

Beneficial skew

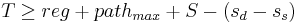

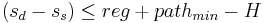

Clock skew can also benefit a circuit by increasing the clock period locally at which the circuit will operate correctly. For each source register and destination register connected by a path, the following inequalities must hold:

where

- T is the clock period,

- reg is the source register's clock to Q delay,

is the path with the longest delay from source to destination,

is the path with the longest delay from source to destination,- S is the setup time of the destination register

is the path with the shortest delay from source to destination,

is the path with the shortest delay from source to destination,- H is the hold time of the destination register,

represents the clock skew from the source to the destination registers,

represents the clock skew from the source to the destination registers, is the clock skew to the destination register, and

is the clock skew to the destination register, and is the clock skew to the source register.

is the clock skew to the source register.

Positive clock skews are good for fixing setup violations, but can cause hold violations.

On a network

On a network such as the internet, clock skew describes the difference in time shown by the clocks at the different nodes on the network. It is usually an unavoidable phenomenon (at least if one looks at milli-second resolutions), but clock skew of tens of minutes or more is also quite common. Network operations that require time stamps which are comparable across hosts can be affected by clock skew. A number of protocols (e.g. Network Time Protocol) have been designed to reduce clock skew, and produce more stable functions. Some applications (such as game servers) may also use their own synchronization mechanism to avoid reliability problems due to clock skew.

Interfaces

Clock skew is the reason why at fast speeds, serial interfaces (e.g. Serial Attached SCSI or USB) are preferred over parallel interfaces (e.g. parallel SCSI).

See also

References

- Friedman, E.G., ed., Clock Distribution Networks in VLSI Circuits and Systems, IEEE Press, 1995.

- Maheshwari, N., and Sapatnekar, S.S., Timing Analysis and Optimization of Sequential Circuits, Kluwer, 1999.

- Tam, S., Limaye, D.L., and Desai, U.N., "Clock Generation and Distribution for the 130-nm Itanium 2 Processor with 6-MB On-Die L3 Cache", in IEEE Journal of Solid-State Circuits, Vol. 39, No. 4, April 2004.